|

■後藤弘茂のWeekly海外ニュース■画期的なリーク電流制御技術「LongRun2」 |

●Transmetaの切り札はLongRun2とEfficeonの組み合わせ

|

LongRun2は、従来のLongRunを拡張した省電力技術ではない。Transmetaが開発したとしているのは、全く異なるレベルでチップの電力消費を抑える画期的な技術だ。

従来のLongRunのように、CPUの動作周波数と電源電圧(Vdd)を動的に変更するだけでなく、トランジスタのしきい電圧(VtまたはVth)も動的に上げることで、サブスレッショールドリーク(漏れ)電流(Subthreshold Leakage)を下げる。これにより、半導体業界全体が抱えている、消費電力や遅延ばらつきの増大の問題を解決する。「低消費電力チップだけでなく、今後のプロセス世代では誰もが必要とする技術となる」とTransmetaのDavid R. Ditzel氏(創業者兼CTO)は主張する。

TransmetaはLongRun2を新世代CPU「Efficeon TM8000」に実装するだけでなく、他社にもライセンスしていこうとしている。もし、LongRun2がTransmetaの主張する通りの画期性を持つとしたら、この技術がTransmetaを大きく浮上させる可能性があるかもしれない。

Transmetaもその点は十分意識している。先週のMicroprocessor Forumでのプレゼンテーションでも、Ditzel氏はLongRun2の説明を、わざわざ別立てで行なった。また、続くEfficeon発表会でも、LongRun2を大きくピックアップして説明するという念の入れよう。なのに、技術的な詳細は一切、公式の場では明かさないという秘密主義。

そうしたTransmetaの態度からは、同社のLongRun2への期待の高さが伺える。

●半導体業界の悩みのタネはリーク電流

|

| トランジスタのリーク電流 PDF版はこちら |

0.13μmプロセスまでは、動的な消費電力をどう下げるかがテーマで、解決手段としてはチップの動作周波数とVddを動的に制御する技術が編み出された。TransmetaのLongRunや、Intelの拡張版SpeedStep(Geyserville-2)、AMDのPowerNOW!などがそれにあたる。

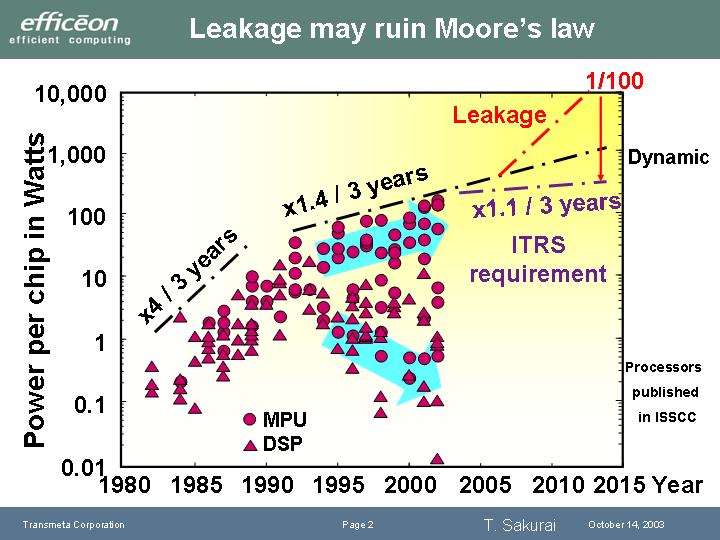

しかし、0.13μm以降、この消費電力の問題は質的な変化を遂げ、従来の省電力技術(LongRun/SpeedStep/PowerNOW!)では解決できなくなりつつある。それは、電力消費の最大の源が、トランジスタのリーク電流になりつつあるからだ。

プロセスが微細化するに連れて、トランジスタのリーク電流は増大する一方だ。90nm世代のハイエンドCPUでは、TDP(Thermal Design Power:熱設計消費電力)の数10%がリーク電流になると言われている。そのため、Vddを動的に減らしても、リーク電流を抑えない限り、どんどん電力が消費されてしまうという状況にある。つまり、ダイナミック電力よりスタティック電力が支配的になって来たため、LongRun/SpeedStepのようなVddスケーリングの効果は薄れてきてしまったわけだ。

●リーク電流削減ではしきい電圧が重要に

|

| Transmeta CTO David R. Ditzel氏 |

「IntelやAMDは、非常に低いしきい電圧(Low Vt)で、最大の周波数を得られるようにしている。しかし、そのためにスタンバイ電力は非常に大きい。一方、携帯機器向けチップなどはVtを非常に高くして、スタンバイ電力を抑えているが、CPUが非常に遅くなっている。Transmetaは、Intelよりしきい電圧(Vt)が高いがそれほど極端ではない。Intelほど高周波数にはできないが、低いスタンバイ電力を実現できる。問題は、このしきい電圧(Vt)が製造時にひとつの値にセットされてしまうことにあった」とDitzel氏は言う。

実際には、細かく言うと、現在は異なるVtのトランジスタを、チップ上で組み合わせることで低消費電力化を図っている。各トランジスタのVtは固定されているため、高速が必要な回路にはLow Vtトランジスタを、低速でも構わない回路にはHigh Vtトランジスタを使っている。しかし、Vtが固定されていることは変わらない。

●Vtを動的に制御するのが次のステップ

|

| MPFで行なわれたLongRun2のビデオによるデモ。144mWが2mWまで下がる様子がデモされた |

つまり、LongRunやSpeedStepで負荷に応じてCPUの電源電圧を制御するのと同じように、チップの動作速度に応じてVtを制御するというわけだ。LongRunやSpeedStepがVddスケーリングなら、今度は同じようにVtスケーリングをしようとしている。こうした手法では、CPUに高速性が要求される時はVtを下げてリーク電流は多いが高速なトランジスタにし、CPUのアイドル時にはVtを上げて低速だがリーク電流を抑えたトランジスタにする。

実際、こうしたアプローチの研究はここへ来て急増している。しきい電圧(Vt)を可変にして動的に変化させる回路技術は、多くの大学や企業が研究している。「VT-CMOS(Variable Threshold CMOS)」と呼ばれる技術などが知られている。また、Intelにしても2002年のISSCCで、トランジスタのボディ領域にかける電圧を制御することで電位差を変化させる「Body Bias」系技術を発表している。

Transmetaは自社の技術内容をまだ明かしていないが、同社のアプローチもこうしたラインに沿ったものであるのは明らかだ。実際、Efficeonの発表では、この問題についての研究で知られる東京大学の桜井貴康教授がビデオで登場した。桜井氏は、今年2月のISSCCでも特別講演を行ない、スタティック電力を減らすしきい電圧制御技術などについて示していた。

|

|

| 桜井氏のプレゼンテーションで示された増大する一方のトランジスタのリーク電流の図 | 同じく、リーク電流により増大するチップの消費電力の図 |

「桜井氏はこの問題を研究しており、我々も一緒にやって来た。そして、桜井氏もTransmetaのアプローチは非常に新しいと指摘している。もちろん、我々も過去の研究から多くを借りているが、LongRun2はそれをさらに発展させたユニークなものだ」とDitzel氏は語る。

LongRun2について、現在公式に明らかにされているのは、LongRun2に対応したEfficeonでは、動的にトランジスタのVtをアジャストすることで、リーク電流を大幅に削減するということ。スタンバイ時には、ほとんどのリーク電流はなくなると言う。

例えば、LongRun2をディセーブルにした状態ではEfficeonのスタンバイ時リーク電流は144mWだが、LongRun2をイネーブルにするとそれが2mWにまで下がるという。つまり、1/70にまでリーク電流を削減することが可能になるわけだ。ほとんど組み込みCPUのリーク電流レベルにまで落とす。その結果、CPUのアクティブ消費電力も、待機時消費電力もどちらも下げることができ、TDP(Thermal Design Power:熱設計消費電力)と平均消費電力を下げることが可能になるという。

LongRun2については、明日も引き続きこのコラムでレポートする。

□関連記事

【10月18日】【笠原】90nmプロセスとLongRun2で復活をかけるTransmeta

http://pc.watch.impress.co.jp/docs/2003/1018/ubiq29.htm

【10月15日】【MPF】ついにベールを脱いだTransmetaの秘密兵器Efficeon!

http://pc.watch.impress.co.jp/docs/2003/1015/mpf0f1.htm

(2003年10月22日)

[Reported by 後藤 弘茂(Hiroshige Goto)]

【PC Watchホームページ】

PC Watch編集部 pc-watch-info@impress.co.jp 個別にご回答することはいたしかねます。

Copyright (c) 2003 Impress Corporation All rights reserved.