|

■後藤弘茂のWeekly海外ニュース■LongRun2のライセンス戦略に出るTransmeta |

●LongRun2では回路設計とプロセス技術も拡張

|

| TM8000のテストボード |

まず、LongRun2では、リーク電流削減のために、トランジスタのしきい電圧(Vt)制御を行なう。しかし、そのためには、次世代CPU「Efficeon TM8000」にそのための回路設計などを用意しなければならない。それについてDitzel氏は次のように語る。

「LongRun2には異なる洗練度のステップがある。もっとも低いレベルの機能は、特殊な回路技術を必要としない。実際、ラボで行なったLongRun2の最初の実験ではCrusoeチップも使ったが、それは特殊回路を使わないものだった。

だが、特殊な回路技術を組み合わせた方がLongRun2はずっとうまく働く。だから、Efficeonで実現しようとしているのは、特殊回路を組み合わせたものだ。そのレベルのLongRun2は、実際には、3つの要素を必要とする。

ひとつは、特別な回路設計。もうひとつはFabでの製造方法で、シリコンウェハーも多少異なる。最後がソフトウェア。回路設計やシリコンの変更が必要なのは、しきい電圧(Vt)の制御のために、ソフトウェアが専用回路経由でトランジスタと話をする必要があるからだ」

つまり、フル機能のLongRun2はソフトウェアだけでなく、回路設計技術やシリコン技術との組み合わせになるわけだ。ちなみに、Efficeonは最初のバージョンから、必要な回路はすでに組み込まれているという。

●Transmetaは実装が容易と主張

|

| トランジスタのリーク電流 PDF版はこちら |

「多くの業界人が、Vtの制御を行なうためには、Fab側に非常に特殊なプロセスが必要になると考えている。また、新たに大規模な特殊回路の追加が必要で、かなりの規模のチップ再設計なしには不可能だと考えている。

しかし、当社の技術は違う。例えばシリコンについては、我々の方法では、多少の変更は必要となるが、依然としてバルクCMOSで実現可能だ。また、しきい電圧(Vt)をp型とn型のどちらのトランジスタでも制御できる。また、LongRun2に必要な特殊回路も、非常に小さな数で、チップ上で占有する面積も極限られている。そのため、我々の方法ではチップを大幅に再設計する必要がない。

正直な話をすると、じつは当社も1年ほど前までは従来型の技術を研究していた。しかし、1年前に、Transmetaは、従来の方式とは非常に異なる、実践的(practical)な方法を発見した。practicalという英語は非常に重要だ。それは、余計な労力をあまりかけずに非常に簡単に製造できることを意味する。

だから、当社のチップを、この制御方法を使えるように比較的簡単にモディファイできた。将来はどんなチップもこの種のリーク電流制御を持てるようになると確信を持っている」

また、LongRun2はVtを個別に制御するというだけではない。他にもリーク電流を抑えるためのテクニックを組み合わせたものになる。

「半導体の物理的な特性とリーク電流については、半導体Fabは熟知している。ところが、彼らもチップのコンディションが変わった場合のことは、把握できていない。例えば、チップの温度が上がると、リーク電流はぐっと悪くなる。だから、チップ温度が上昇したらクールダウンすれば、リーク電流も抑えることができる。

問題は、熱などの影響をいかにモデル化するかになる。我々はそれも行なった。CPUのソフトレイヤCMS(Code Morphing Software)が、チップ動作時の物理特性の変化を把握し、均衡状態に保つようにすることができる」(Ditzel氏)

また、チップのリーク電流問題には、この他ゲートリーク電流(ゲートへの電流の漏れ)もある。この問題へのソリューションでは、High-kゲート素材が研究されているが、今のところトランジスタ速度を遅くせずに有効な素材は完成していない。Ditzel氏は、同社がこの問題に対しても何らかの技術を研究していることを示唆する。

●半導体設計では重要となるVt制御

また、Ditzel氏はVtの制御は、消費電力を低減するだけでなく、今後の半導体では歩留まりの維持でも重要な技術になるかもしれないと指摘する。

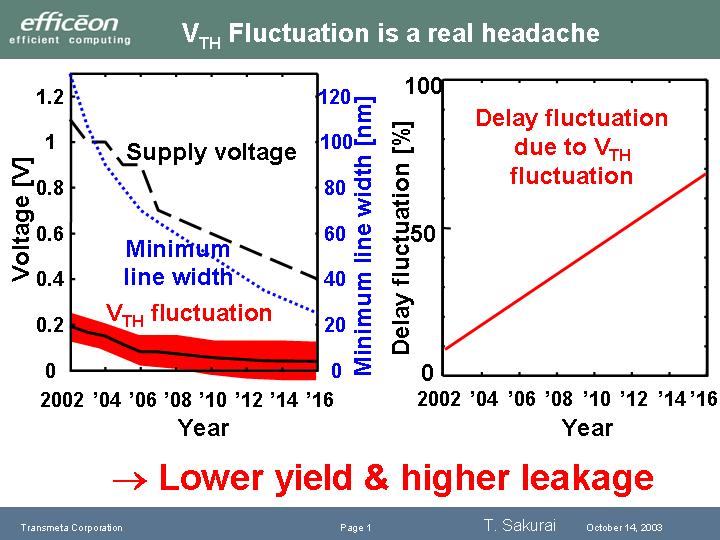

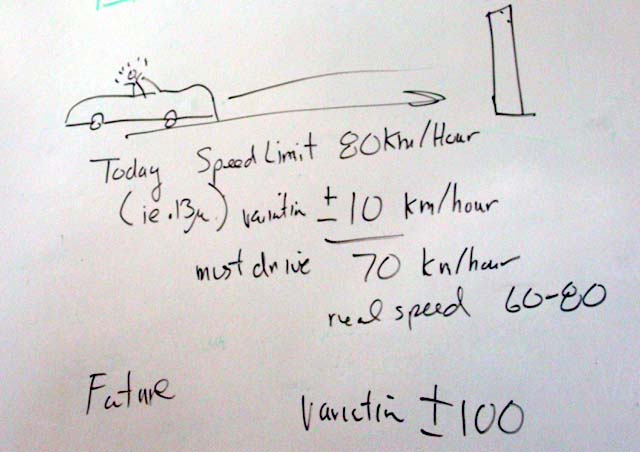

「東京大学の桜井貴康教授が、ゲートディレイのばらつきについて、非常に面白い指摘をしている。今後は、プロセス世代毎に製造時のVtのばらつきがどんどん大きくなっていくために、(トランジスタ毎に)ディレイにもばらつきが生じてしまう。この問題はクルマに例えるとわかりやすい。

例えば、制限速度80km/hの道路を走る車を設計するとしよう。その場合は、スピードのばらつきを80km/hの枠内に抑える必要がある。速度にばらつきが+-10km/hあるとすると、ターゲットを70km/hにして、実際の走行速度を60~80km/hにすることになる。この程度なら、少し遅くはなるが大丈夫だ。

しかし、ばらつきがどんどん大きくなり、+-100kmになったらどうなるか? 時速20km/hでバックするクルマを設計しなくてはならなくなる(笑)。これが大きな問題だ。実際の半導体でも同じで、将来、現実問題としてしきい電圧(Vt)は0V以下になってしまう可能性がある。ばらつきが+-50%になってしまったら、もうチップ設計はできない。これが近い将来やってくる問題だ。

この問題に、第一線のエンジニア達はもう気がついている。しかし、企業の副社長達は5年前の知識をもとに、問題がないと思っている。だから、彼らはチップをどんどん速くするように言っているが、実際には大きな壁が迫りつつあるわけだ。

だから、この問題は、誰にとっても重大な問題だ。0.13μmでもVtには若干のばらつき問題があったが、90nmではさらに大きくなり、65nmでは頭痛のタネになるだろう。だから、我々はこの技術が発展すると考えている」

つまり、ばらつきが大きくなるため、規定の枠内で動作するチップが少なくなり、歩留まりが悪化してしまうというわけだ。

じつは、この問題は、Intelも2002年のISSCC(IEEE International Solid-State Circuits Conference)の際に指摘している。Intelはその解決策として小ブロックでしきい電圧を制御する「Adaptive Body Bias」でばらつきを抑えることで、歩留まりを上げるというアプローチを発表していた。つまり、Transmetaだけでなく、業界全体で、ほぼ同じ方向を向いているわけだ。

|

|

| 桜井氏のプレゼンテーションで示された、増大するVtのばらつきにより拡大するゲートディレイのばらつき | 、Ditzel氏によるVtのばらつきを自動車に例えたメモ |

●LongRun2によって高リーク電流プロセスの採用へ

Transmetaは、Efficeonの製造については、ファウンドリであるTSMCと富士通で、この技術を使うという。

「面白かったのは、我々が富士通と最初にこの(Efficeonの製造委託)話をし始めた時、互いにまだ相手をよくわかっていなかった。それで、富士通側はTransmetaは低消費電力チップの会社だから、当然、低リーク電流のトランジスタを望むだろうと考えた。ところが、我々は『いや、高リーク電流のトランジスタが欲しい』と言ったんだ。低リーク電流バージョンだと、Vtが高いためにトランジスタが低速だからだ。富士通が驚いて、それだと消費電力が高くなると言ってきたので『それはOKだ。我々はリーク電流を制御できるから』と答えたら、ますます驚いていた。

我々は、LongRun2でリーク電流を制御するので、高リーク電流で高速なトランジスタでも使うことができる。余計なリーク電流が発生するのは、ピークパフォーマンスの時だけだからだ。我々が使うのは、富士通がハイエンドのSPARC 64プロセッサを作っているのとほぼ同じプロセスだ」

また、Ditzel氏は、同技術が、半導体Fabにとっても魅力だと力説する。

「リーク電流の問題で、今後はプロセスを微細化してもトランジスタを速くできなくなってしまう。そうしたら、顧客側はプロセスを移行する理由がなくなってしまう。新Fabのコストは20億ドルに達している。もし、顧客が新Fabを使う理由がないと言い始めたら、Fabは20億ドルの頭痛を抱える。Transmetaは、その頭痛を取り去ることができる」

こうした背景から、Transmetaは今回は、自社の技術を自社製品だけに適用して競争力を高めるのではなく、技術自体も切り売りする方針に切り替える。LongRun2については、他社へのライセンスも考えるという。

「ライセンスに対する答えはイエスだ。可能性はある。まだ公式に決定を下したわけではないが、すでに多くの企業から問い合わせが来ている。人々は、この技術をTransmetaのチップだけでなく、他のチップにも応用できると考えている。我々もそう考えている。

Intelから問い合わせが来たら? (笑) そういうこともあるかもしれない。しかし、我々はまず日本の企業にこの技術を提供していきたいと考えている」

Ditzel氏は、このように、日本企業と接触があることを匂わす発言をする。

Transmetaが、もしうまくLongRun2のライセンスに成功すれば、それは売り上げ伸び悩みで苦しむ同社にとって突破口になる。Ditzel氏の口ぶりからは、Transmetaのそうした思惑がうかがえる。

□関連記事

【10月22日】【海外】画期的なリーク電流制御技術「LongRun2」

http://pc.watch.impress.co.jp/docs/2003/1022/kaigai035.htm

【10月18日】【笠原】90nmプロセスとLongRun2で復活をかけるTransmeta

http://pc.watch.impress.co.jp/docs/2003/1018/ubiq29.htm

【10月15日】【MPF】ついにベールを脱いだTransmetaの秘密兵器Efficeon!

http://pc.watch.impress.co.jp/docs/2003/1015/mpf0f1.htm

(2003年10月23日)

[Reported by 後藤 弘茂(Hiroshige Goto)]

【PC Watchホームページ】

PC Watch編集部 pc-watch-info@impress.co.jp 個別にご回答することはいたしかねます。

Copyright (c) 2003 Impress Corporation All rights reserved.